작성: Eric Rutulis, John Scott-Thomas, PhD

이 내용은 IEDM 2021에서 소니가 1차 발표한 결과를 기반으로 2022 VLSI 에서 추가로 업데이트 한 내용입니다. TechInsights는 "세계 최초" 2층 이미지 센서를 처음으로 살펴보았으며 이 분석한 결과를 공유합니다.

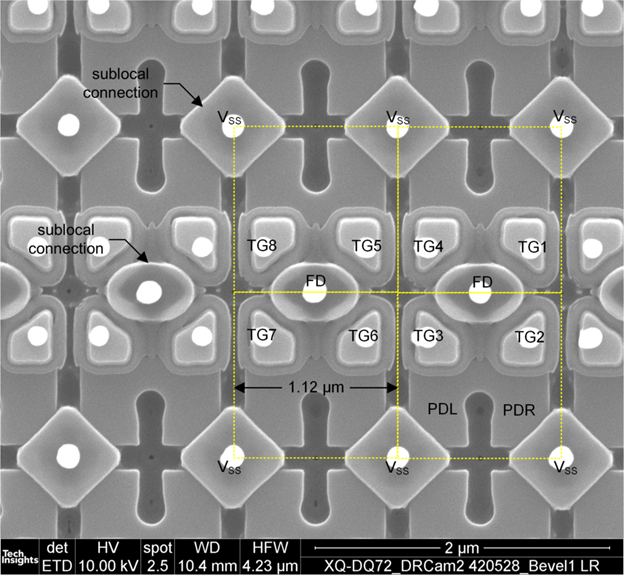

이 장치는 48MP, 1.12µm 픽셀 피치를 가진 Sony Xperia 1V 스마트폰 메인 카메라에 적용 되었으며, 듀얼 포토다이오드(풀 어레이 PDAF의 경우 각 픽셀에 왼쪽 및 오른쪽 포토다이오드)가 있음을 확인할 수 있습니다. 다이 크기는 가장자리에서 가장자리까지 11.37 x 7.69mm입니다.

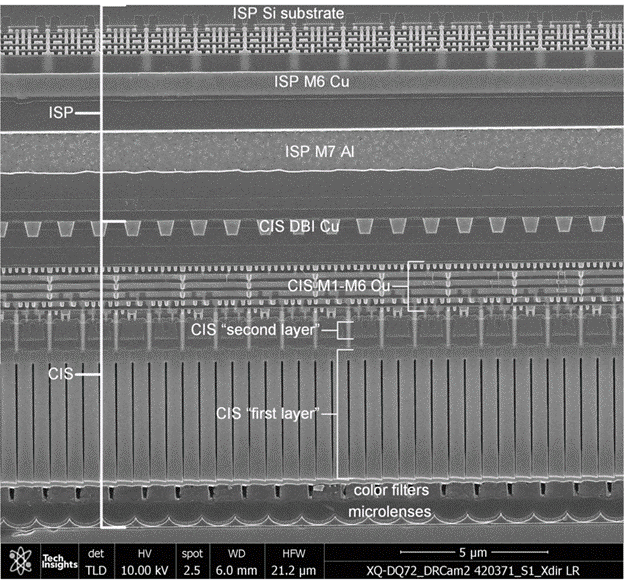

실제로 이 센서는 3개의 실리콘 레이어로 구성되어 있으며, "세 번째 레이어" 이미지 신호 프로세서(ISP)는 "두 번째 레이어" (가능한 경우 Sony의 명명법을 사용함)에 직접 결합 인터페이스(DBI)를 사용하여 적층되었습니다.

그림 1은 SEM 단면을 보여줍니다. 빛은 마이크로렌즈와 컬러 필터를 통해 이미지 하단에서 들어옵니다. 각 픽셀은 양자 효율을 높이기 위해 Air 그리드(복합 레이어 포함)로 분리됩니다. Front Deep Trench Isolation은 각 포토다이오드 사이에 사용되며, Sony는 전체 우물 용량과 양자 효율을 개선하기 위해 깊은 트렌치에서 SiO2를 사용하고 있는 것으로 보입니다(이는 추가 분석을 통해 확인될 예정임).

이 층에는 다이오드에서 플로팅 디퓨전으로 광전하를 전송하는 데 사용되는 평면 전송 게이트도 있습니다. 첫 번째 레이어 위에는 각 픽셀에 대해 3개의 트랜지스터를 포함하는 실리콘의 "두 번째 레이어"가 있습니다. 이 3개의 트랜지스터는 Reset, Amp(Source-Follower) 및 Select 트랜지스터를 의미합니다.

이 트랜지스터는 두 번째 레이어 실리콘 위에 위치하며 기본적으로 TSV(Through Silicon Vias)를 형성하여 두 번째 레이어를 통과하는 "딥 컨택트"을 사용하여 포토다이오드가 있는 첫 번째 레이어에 연결이 이루어집니다.

마지막으로 ISP는 하이브리드(직접) 본딩을 사용하여 연결된 두 번째 레이어 금속면 위에 위치합니다. CIS DBI Cu에 연결하는 데 사용되는 ISP의 구리는 이 이미지에서 보이지 않습니다.

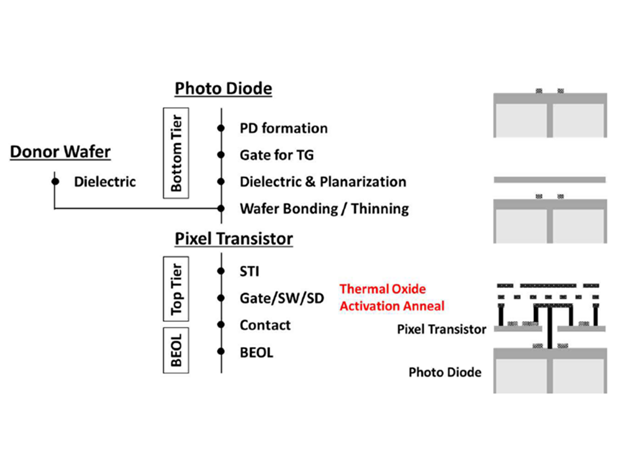

이 구조의 핵심은 두 번째 레이어에서 임플란트를 활성화하는 데 필요한 Thermal 효과를 견딜 수 있는 공정 흐름입니다. Sony는 프로세스 흐름을 어느 정도 자세히 설명했습니다( IEDM 2021, "3D Sequential Process Integration for CMOS Image Sensor" ).

그림 2는 프로세스 흐름을 보여주는 그림입니다. 첫 번째 레이어 포토다이오드와 Transfer Gate가 형성되고 두 번째 레이어는 웨이퍼 본딩 후 박막화(Wafer Thinning)됩니다. 그래야만 두 번째 층 게이트 산화물이 형성되고 임플란트가 활성화됩니다.

그림 2: "CMOS 이미지 센서를 위한 3D 순차 공정 통합", IEDM 2021에 설명된 2계층 CIS의 공정 흐름.

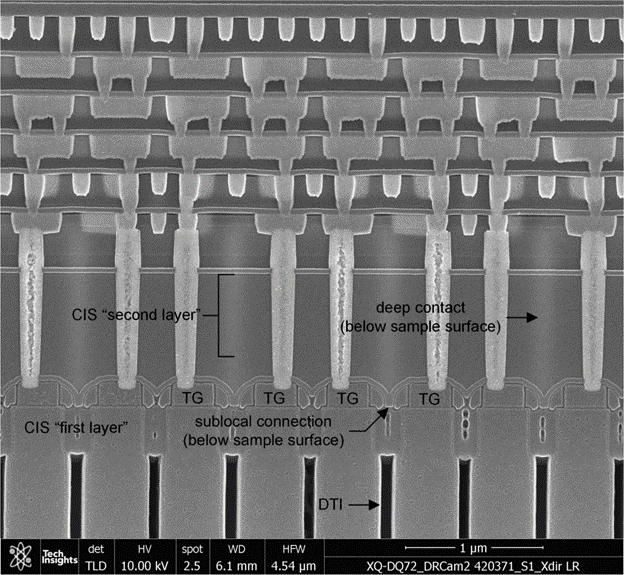

첫 번째 레이어와 두 번째 레이어 사이의 인터페이스는 그림 3에 자세히 나와 있습니다. Transfer Gate(이미지의 TG)는 두 번째 레이어의 첫 번째 금속 레이어에 연결됩니다. 약간 더 긴 깊은 접점은 샘플 표면 아래에 있으며 이미지에서 부분적으로 볼 수 있습니다. 이들은 첫 번째 레이어와 두 번째 레이어 사이의 플로팅 확산 노드를 연결합니다. 서브로컬 연결(샘플 표면 아래)은 첫 번째 레이어 바로 위에 있는 4개의 포토다이오드를 Reset FET의 소스와 AMP(Source-Follower) FET의 게이트에 상호 연결하는 데 사용됩니다.

하위 로컬 연결은 그림 4에서 자세히 살펴하게 보입니다. 이것은 기판 수준에서 첫 번째 레이어의 평면 SEM 이미지입니다. 노란색 상자는 픽셀의 윤곽을 나타내며 PDL 및 PDR은 왼쪽 및 오른쪽 포토다이오드를 나타냅니다. 하나의 마이크로렌즈가 각 픽셀을 덮습니다. 하위 로컬 연결이 표시되며 2픽셀용 플로팅 디퓨전과 4픽셀용 접지를 상호 연결하는 데 사용됩니다. 하위 로컬 연결은 폴리실리콘인 것으로 보입니다. 이것은 현재 추가 분석을 통해 확인되고 있습니다.

그림 4: 기판 레벨에서 픽셀 1층의 SEM 평면도.

'Main > Breaking News' 카테고리의 다른 글

| SK Hynixs 의 CIS 비지니스 재편 신호 (1) | 2024.12.16 |

|---|---|

| Samsung Galaxy 에 양자 암호 Chip 탑재 (1) | 2023.07.14 |

| 새로운 프로그램 언어 Mojo 등장 (1) | 2023.06.12 |

| Nvidia 차세대 GPU, Hopper(H100) 선주문가 4,730 만원 (1) | 2023.06.07 |

| 벨기에 VoxelSensors, 3D 인식을 통한 물리 현실과 디지털 세계를 융합하는 기술로 65억 원(5M 유로)의 시드 펀딩 확보 발표 (0) | 2023.06.04 |